## Automotive LIN bus ESD protection in SOD323

SOD323 (SC-76)

#### **Product status link**

ESDLIN1524BJ

#### **Features**

- AEC-Q101 qualified

- · Asymetrical bidirectional ESD protection

- Low leakage current (I<sub>R</sub> max. < 50 nA at V<sub>RM</sub>)

- Stand-off voltage:

- -15 V (to comply with reverse battery)

- +24 V (to comply with jump start)

- High ESD protection level: up to 30 kV

- ECOPACK2 RoHS compliant component

#### Complies with the following standards

- UL94, V0

- J-STD-020 MSL level 1

- IPC7531 footprint and JEDEC registered package

- ISO 16750-2 (jump start and reversed battery tests)

- ISO 10605 C = 150 pF, R = 330 Ω:

- ±30 kV (air discharge)

- ±30 kV (contact discharge)

- ISO 10605 C = 330 pF,  $R = 330 \Omega$ :

- ± 30 kV (air discharge)

- ± 30 kV (contact discharge)

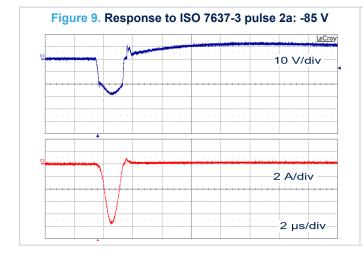

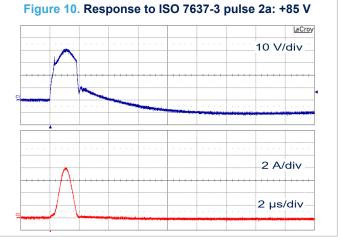

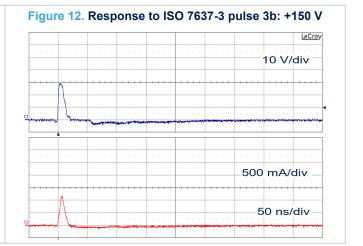

- · ISO 7637-3:

- Pulse 3a: -150 V

- Pulse 3b: +150 V

- Pulse 2a: +/- 85 V

- ISO 17987-7 (LIN bus)

- SAE J3076 (CXPI bus)

### **Description**

The ESDLIN1524BJ is an asymmetrical TVS diode designed to protect one local interconnect network (LIN) bus and clock extension peripheral interface (CXPI) against electrostatic discharge (ESD) and other transient surges such as those defined in ISO 7637-3.

The SOD323 is a small package that saves space on high density printed circuit board.

## 1 Characteristics

Table 1. Absolute maximum ratings (T<sub>amb</sub> = 25 °C)

| Symbol           |                                                        | Value                              | Unit |     |  |

|------------------|--------------------------------------------------------|------------------------------------|------|-----|--|

|                  |                                                        | ISO 10605 - C = 150 pF, R = 330 Ω: |      |     |  |

|                  | Peak pulse voltage                                     | Contact discharge                  | ±30  | 107 |  |

| V                |                                                        | Air discharge                      | ±30  |     |  |

| V <sub>PP</sub>  |                                                        | ISO 10605 - C = 330 pF, R = 330 Ω: |      | kV  |  |

|                  |                                                        | Contact discharge                  | ±30  |     |  |

|                  |                                                        | Air discharge                      | ±30  |     |  |

| P <sub>PP</sub>  | Peak pulse power dissipation                           | 160                                | W    |     |  |

| T <sub>stg</sub> | Storage temperature range -65                          |                                    |      | °C  |  |

| Тј               | Operating junction temperature range                   |                                    |      | °C  |  |

| T <sub>L</sub>   | Maximum lead temperature for soldering during 10 s 260 |                                    |      | °C  |  |

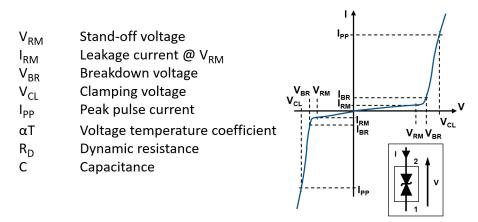

Figure 1. Electrical characteristics (definitions)

DS4896 - Rev 5 page 2/13

| Table 2. Electrical characteristics | $(T_{amb} = 25^{\circ} C, u)$ | inless otherwise specified) |

|-------------------------------------|-------------------------------|-----------------------------|

|-------------------------------------|-------------------------------|-----------------------------|

| Symbol               | Parameter                       | Test                   | Test condition                                   |         | Тур. | Max.                 | Unit   |

|----------------------|---------------------------------|------------------------|--------------------------------------------------|---------|------|----------------------|--------|

| $V_{BR}$             | From pin 2 to pin 1             | l- = 5 mΛ t <          | $I_R = 5 \text{ mA}, t_p < 50 \text{ ms}$        |         | 27.8 | 30.3                 | V      |

| VBR                  | From pin 1 to pin 2             | IR - 3 IIIA, tp <      |                                                  |         | 18.9 | 20.3                 | V      |

| I                    | From pin 2 to pin 1             | V <sub>RM</sub> = 24 V | V <sub>RM</sub> = 24 V<br>V <sub>RM</sub> = 15 V |         | 1    | 50                   |        |

| I <sub>RM</sub>      | From pin 1 to pin 2             | V <sub>RM</sub> = 15 V |                                                  |         |      | 50                   | nA     |

|                      | From pin 2 to pin 1             |                        |                                                  | 40      |      |                      |        |

| <b>V</b>             | From pin 1 to pin 2             | I <sub>PP</sub> = 3 A  | 0/00                                             |         |      | 50                   | V      |

| $V_{CL}$             | From pin 2 to pin 1             | I <sub>PP</sub> = 1 A  | 8/20 μs                                          | 6/20 μ5 |      | 25                   | V      |

|                      | From pin 1 to pin 2             | I <sub>PP</sub> = 5 A  |                                                  |         |      | 35                   |        |

| С                    | V <sub>R</sub> = 0 V, f = 1 MHz |                        |                                                  |         | 16   | 20                   | pF     |

| αT <sup>(1)(2)</sup> | From pin 2 to pin 1             |                        |                                                  |         | 9.6  | 10 <sup>-4</sup> /°C |        |

| u i (1/(2)           | From pin 1 to pin 2             |                        |                                                  |         |      | 8.8                  | 10 7/2 |

- 1. Connections done according to Figure 2.

- 2. To calculate  $V_{BR}$  or  $V_{CL}$  versus junction temperature, use the following formulas:

- $V_{BR}$  at  $T_J = V_{BR}$  at 25 °C x (1 +  $\alpha T$  x ( $T_J$  25))

- $V_{CL}$  at  $T_J = V_{CL}$  at 25 °C x (1 +  $\alpha T$  x ( $T_J$  25)).

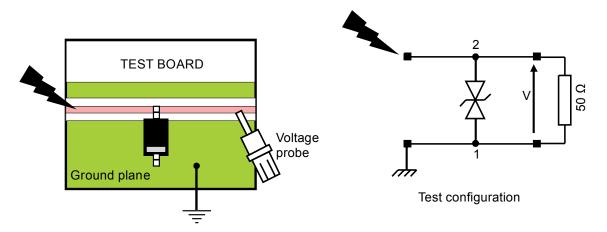

Figure 2. Clamping test conditions

DS4896 - Rev 5 page 3/13

### 1.1 Characteristics (curves)

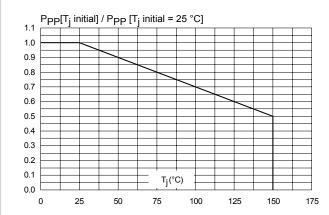

Figure 3. Relative variation of peak pulse power versus initial junction temperature

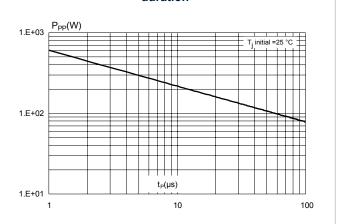

Figure 4. Peak pulse power versus exponential pulse duration

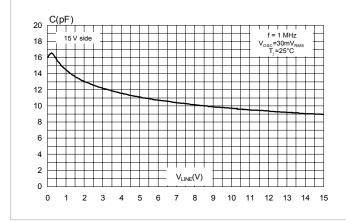

Figure 5. Junction capacitance versus line voltage, 15 V side

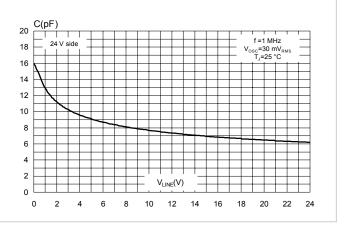

Figure 6. Junction capacitance versus line voltage, 24 V side

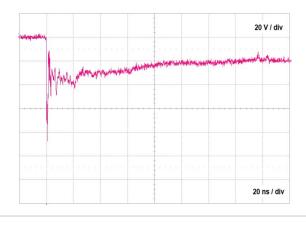

Figure 7. ESD response to ISO 10605 - C = 150 pF, R = 330  $\Omega$  (-8 kV contact discharge)

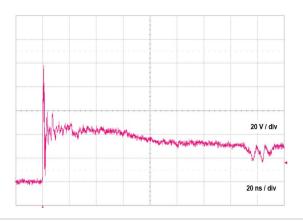

Figure 8. ESD response to ISO 10605 - C = 150 pF, R = 330  $\Omega$  (+8 kV contact discharge)

DS4896 - Rev 5 page 4/13

Figure 11. Response to ISO 7637-3 pulse 3a: -150 V

10 V/div

500 mA/div

DS4896 - Rev 5 page 5/13

## 2 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

## 2.1 Package information

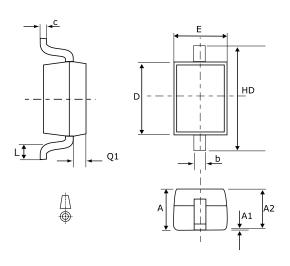

Figure 13. SOD323 package outline

Table 3. SOD323 package mechanical data

|      | Dimensions Millimeters |      |  |  |

|------|------------------------|------|--|--|

| Ref. |                        |      |  |  |

|      | Min.                   | Max. |  |  |

| Α    |                        | 1.17 |  |  |

| A1   | 0.00                   | 0.10 |  |  |

| A2   | 0.93                   | 1.01 |  |  |

| b    | 0.25                   | 0.44 |  |  |

| С    | 0.10                   | 0.25 |  |  |

| D    | 1.52                   | 1.80 |  |  |

| Е    | 1.11                   | 1.45 |  |  |

| HD   | 2.30                   | 2.70 |  |  |

| L    | 0.10                   | 0.46 |  |  |

| Q1   | 0.10                   | 0.41 |  |  |

DS4896 - Rev 5 page 6/13

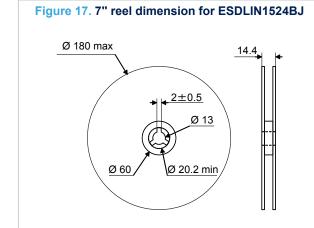

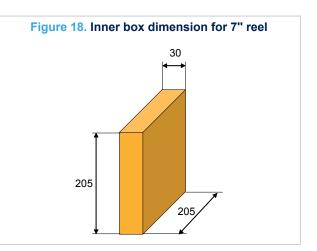

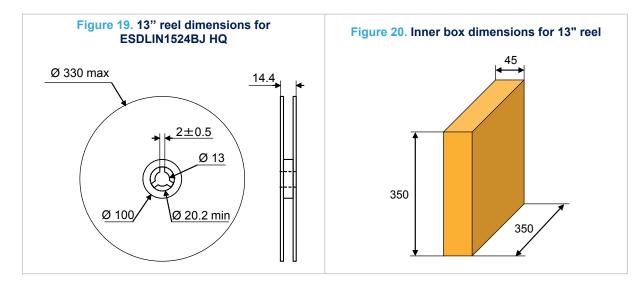

## 2.2 Packing information

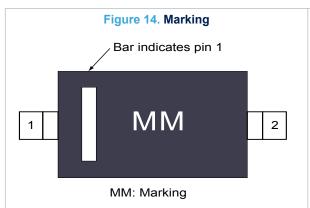

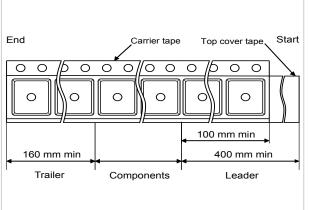

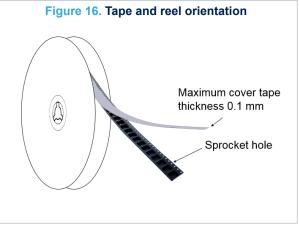

The marking can be rotated by a multiple of  $90^{\circ}$  to differentiate assembly location.

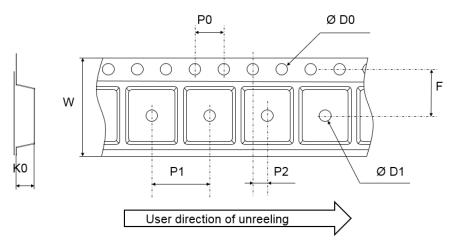

Pin 1 located according to EIA-481

Note: Pocket dimensions are not on scale Pocket shape may vary depending on package

DS4896 - Rev 5 page 7/13

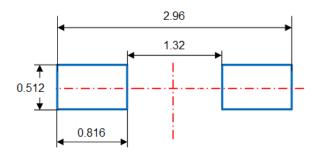

Figure 21. Tape outline

Note: Pocket dimensions are not on scale Pocket shape may vary depending on package

Table 4. Tape dimension values

|      | Dimensions  |      |      |  |  |  |

|------|-------------|------|------|--|--|--|

| Ref. | Millimeters |      |      |  |  |  |

|      | Min.        | Тур. | Max. |  |  |  |

| D0   | 1.50        | 1.55 | 1.60 |  |  |  |

| D1   | 1.00        |      |      |  |  |  |

| F    | 3.45        | 3.50 | 3.55 |  |  |  |

| К0   | 1.12        | 1.22 | 1.32 |  |  |  |

| P0   | 3.90        | 4.00 | 4.10 |  |  |  |

| P1   | 3.90        | 4.00 | 4.10 |  |  |  |

| P2   | 1.95        | 2.00 | 2.05 |  |  |  |

| W    | 7.90        | 8.00 | 8.30 |  |  |  |

DS4896 - Rev 5 page 8/13

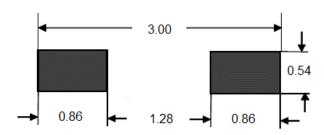

## 3 Recommendations on PCB assembly

## 3.1 Footprint

Figure 22. Recommended footprint in mm

## 3.2 Stencil opening design

Stencil opening thickness: 75 to 125  $\mu m$  / 3 to 5 mils

Pad stencil aperture ratio: 90%

Figure 23. Stencil opening recommendations

DS4896 - Rev 5 page 9/13

### 3.3 Solder paste

- 1. Halide-free flux, qualification ROL0 according to ANSI/J-STD-004.

- 2. "No clean" solder paste recommended.

- 3. Offers a high tack force to resist component movement during high speed.

- 4. Use solder paste with fine particles: powder particle size is 20-38 μm.

#### 3.4 Placement

- 1. Manual positioning is not recommended.

- It is recommended to use the lead recognition capabilities of the placement system, not the outline centering.

- 3. Standard tolerance of  $\pm 0.05$  mm is recommended.

- 4. 1.0 N placement force is recommended. Too much placement force can lead to squeezed out solder paste and cause solder joints to short. Too low placement force can lead to insufficient contact between package and solder paste that could cause open solder joints or badly centered packages.

- 5. To improve the package placement accuracy, a bottom side optical control should be performed with a high resolution tool.

- For assembly, a perfect supporting of the PCB (all the more on flexible PCB) is recommended during solder paste printing, pick and place and reflow soldering by using optimized tools.

### 3.5 PCB design preference

- 1. To control the solder paste amount, the closed via is recommended instead of open vias.

- 2. The position of tracks and open vias in the solder area should be well balanced. A symmetrical layout is paste printing, pick and place and reflow soldering by using optimized tools.

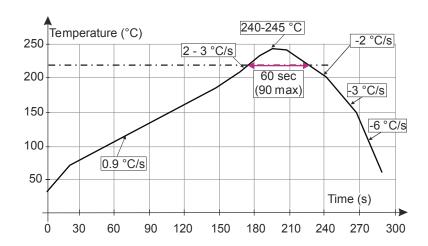

### 3.6 Reflow profile

Figure 24. ST ECOPACK recommended soldering reflow profile for PCB mounting

Note: Minimize air convection currents in the reflow oven to avoid component movement. O<sub>2</sub> rate inside the oven must be below 500 ppm. Maximum soldering profile corresponds to the latest IPC/JEDEC J-STD-020.

DS4896 - Rev 5 page 10/13

## 4 Ordering information

Table 5. Ordering information

| Order code      | Marking <sup>(1)</sup> | Package | Weight | Base qty. | Delivery mode |

|-----------------|------------------------|---------|--------|-----------|---------------|

| ESDLIN1524BJ    | 24                     | SOD 323 | 5 mg   | 3000      | Tape and reel |

| ESDLIN1524BJ-HQ | 24                     | SOD 323 | 5 mg   | 10000     | Tape and reel |

<sup>1.</sup> The marking can be rotated by multiples of 90° to differentiate assembly location

DS4896 - Rev 5 page 11/13

## **Revision history**

Table 6. Document revision history

| Date        | Version | Changes                                                                                                                                                                                                                                                                                                     |  |  |

|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 28-Aug-2006 | 1       | Initial release.                                                                                                                                                                                                                                                                                            |  |  |

| 22-Sep-2006 | 2       | Added Figure 6 Placement and layout recommendations                                                                                                                                                                                                                                                         |  |  |

| 18-Jan-2013 | 3       | Updated Table6. Added Figure 10 and Figure 11.                                                                                                                                                                                                                                                              |  |  |

|             |         | Updated title and cover page.                                                                                                                                                                                                                                                                               |  |  |

|             |         | Updated Table 1: "Absolute maximum ratings (limiting values) Tamb = $25^{\circ}$ C" and Table 3: "Electrical characteristics ( $T_{amb}$ = $25^{\circ}$ C)".                                                                                                                                                |  |  |

| 17-Oct-2017 | 4       | Added Figure 8: "Response to ISO 7637-3 pulse 3a (Us = -150 V)", Figure 9: "Response to ISO 7637-3 pulse 3b (Us = 100 V)", Figure 10: "ESD response to ISO 16605 ( C = 150 pF, R = 330 $\Omega$ , 8 kV contact)" and Figure 11: "ESD response to ISO 16605 ( C = 150 pF, R = 330 $\Omega$ , 8 kV contact)". |  |  |

|             |         | Minor text changes to improve readability.                                                                                                                                                                                                                                                                  |  |  |

| 29-Dec-2021 | 5       | Added reel definitions.                                                                                                                                                                                                                                                                                     |  |  |

| 20 200 2021 |         | Minor text changes.                                                                                                                                                                                                                                                                                         |  |  |

DS4896 - Rev 5 page 12/13

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DS4896 - Rev 5 page 13/13

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics:

ESDLIN1524BJ ESDLIN1524BJ-HQ